# Prognostic BIST ™ Library

# Time-Dependent Dielectric Breakdown (TDDB) Prognostic BIST Cell™

## FEATURES AND BENEFITS

- The Ridgetop TDDB Prognostic Built-in Self-Test (BIST) cell acts as an early-warning "sentinel" of an upcoming gate oxide failure condition due to Time-Dependent Dielectric Breakdown (TDDB)

- Power consumption is approximately 600 microwatts

- Size: 500 μm<sup>2</sup> at the 0.13 micron process size

- Prognostic "distance" breakdown can be scalable using design equation

- Detects both hard and soft breakdowns

#### DESCRIPTION

The Ridgetop TDDB Prognostic cell is a pad-limited CMOS leakage detection cell. Its unique and proprietary architecture behaves as an early-warning "sentinel" of upcoming gate oxide failure. The amount of pre-warning is dependent on the prognostic distance, which depends on the area and the stress voltage.

The Ridgetop TDDB cell is designed to be co-located with the host circuit and subjected to the same environmental stresses. These environmental stresses contribute to aging of the circuit and can include over and under voltage conditions, transient spikes, radiation exposure, humidity, and excessive temperature conditions.

The size of the TDDB Prognostic cell is approximately 500  $\mu$ m<sup>2</sup> at the 0.13 micron process size. The cell is co-located on the same substrate as the host circuit, and shares the power and physical environment for optimum tracking of the aging effects. The estimated power consumption of the cell itself is approximately 500 microwatts.

#### **Prognostic Distance**

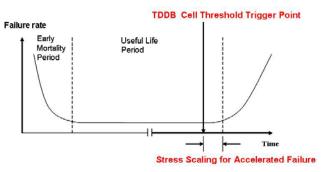

The Prognostic Distance is adjusted by scaling the area of the cell. Ridgetop has nominally set this at 80% of the statistical end-of-life point. This point can be adjusted to some other early indication level. A "picket fence" can also be constructed with multiple cells evenly spaced over the bathtub curve (Figure 1).

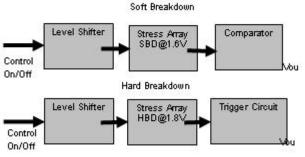

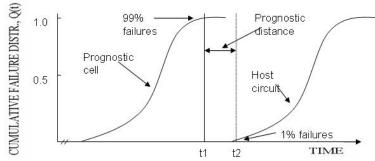

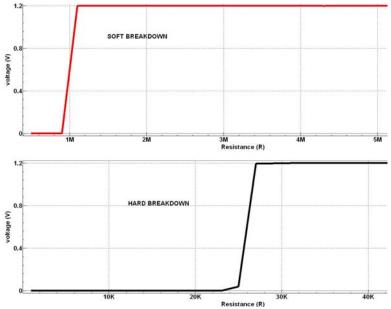

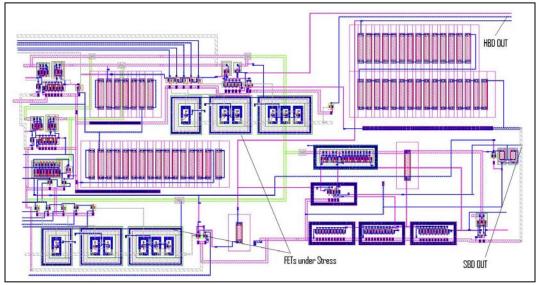

Figure 2 shows the TDDB block diagram; Figure 3 shows failure distribution in a HALT; Figure 4 shows soft and hard breakdown with voltage vs. oxide resistance; and Figure 5 shows a sample TDDB cell layout.

Figure 1: Reliability Bathtub Curve

#### Interfacing

The TDDB cell, as well as other prognostic cells in the Sentinel<sup>™</sup> network, can be configured for a simple buffered logic high or low output to indicate an impending failure event.

## Optional Interfacing using the JTAG Bus Structure

Using the JTAG Toolkit, it is also possible to include a register in a chip design that permits an interface using the standard scan test bus that employs IEEE-1149.1. This interface uses four control lines:

TDI - Test Data In

- TDO Test Data Out

- TCK Test Clock

- TMS Test Mode Select

If the JTAG Toolkit is utilized, the Prognostic cell uses the TDO and TMS lines. The TDO changes its logic state upon a detected failure event and the TMS is used to invoke a "self-test" function to ensure that the cell is functional.

Figure 2: TDDB Block Diagram

Copyright ©2006-2008 Ridgetop Group, Inc.

Figure 3: TDDB Cumulative Failure Distribution in Highly Accelerated Life Test (HALT)

Figure 4: Simulation of TDDB Soft Breakdown and Hard Breakdown, Showing Voltage vs. Oxide Resistance

Figure 5: GDSII Layout of TDDB Cell to Detect Hard and Soft Breakdown