# Reliability Challenges in Through-Silicon Via (TSV)-Based Packaging

Andrew Levy

Ridgetop Group Inc.

August 13, 2014

# Agenda

- Problem Statement

- Interconnect Reliability Background

- TSV BIST Detection Approaches

- SJ BIST Overview

- Precision Current Monitoring Overview

- Summary

**Ridgetop Group**

2

N.

# TSV-based 2.5D & 3D ICs

- Stacking ICs with Through-Silicon Vias (TSVs)

- Circuit density

- Heterogeneous process integration

- Speed/power

- Alternative to Pure "Moore's Law" Improvements

- 3D ICs use TSVs to stack directly on each other

N

- 2.5D ICs stack with an interposer to route signals

- Test methods are both new and extensions to existing

**Ridgetop Group**

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

# Existing Approaches to 2.5D/3D IC Test

- "Known Good Die"  $\rightarrow$  "Pretty Good Die"

- Finding Defects Prior to Shipment

- X-ray, Optical Inspection

- Boundary Scan (IEEE 1149.1)

- IEEE P1838, others

- Limited Focus

- Opens & shorts

- Primarily digital

- Static / low speed operation

- Thermal issues?... Assembly complexities?...

- ...Reliability = Performance Over Time

**Ridgetop Group**

N

# Intermittencies

- Reported electronic system problems in the field cannot be duplicated at the service point or in the lab

- "Three/Four-letter" words (CND, NTF, RTOK)

- Could Not Duplicate (CND)

- No Trouble Found (NTF)

- Retest OK (RTOK)

- 50 to 80% of these CND/NTF/RTOK problem categories are reported by service personnel.

- Major culprits Solder joint intermittencies and NBTI effects in deep submicron ICs

Ridgetop Group Inc 3580 West Ina Road | Tu

West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

12

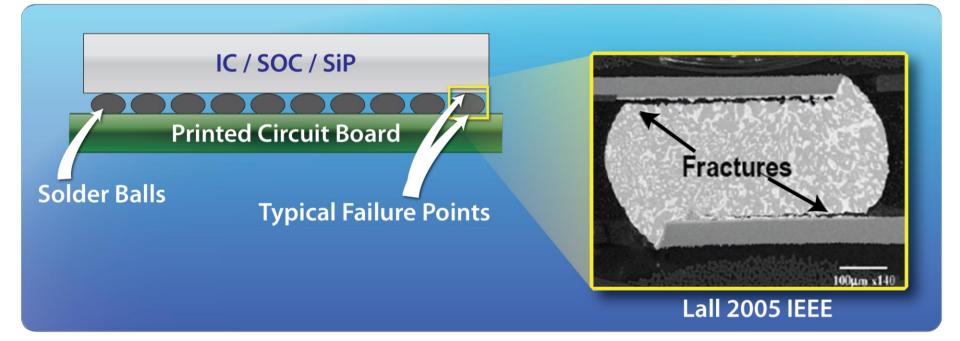

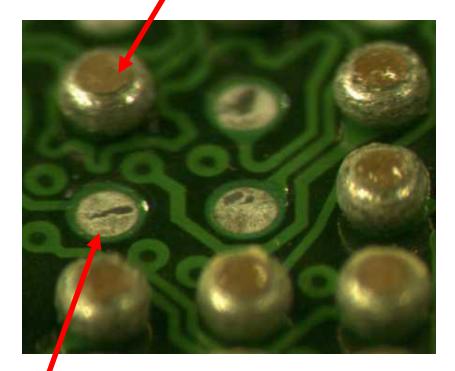

### **BGA Example: Cracks and Fractures**

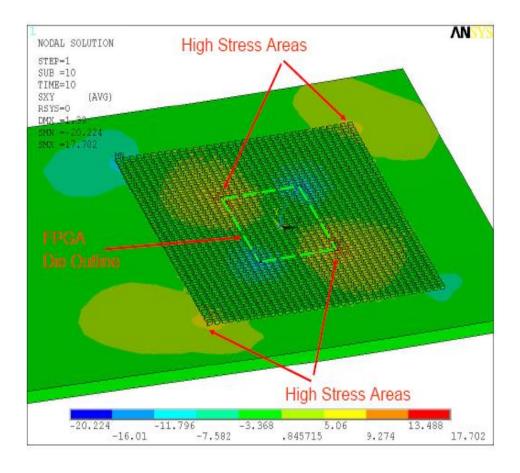

# Defects: Location of Cracks/Fractures

- Corner pins likely to fail first

- High stress areas, and corners of the package and die

**Ridgetop Group** Inc

₩.

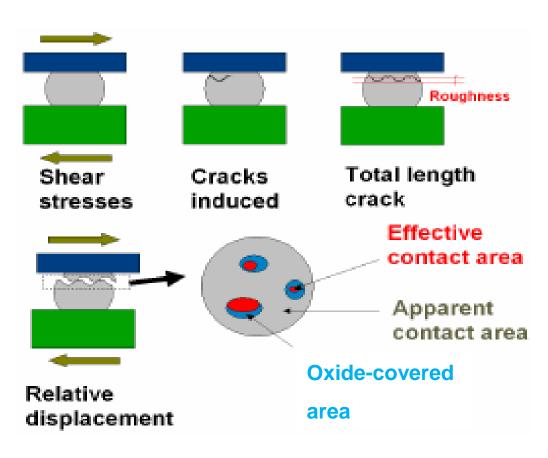

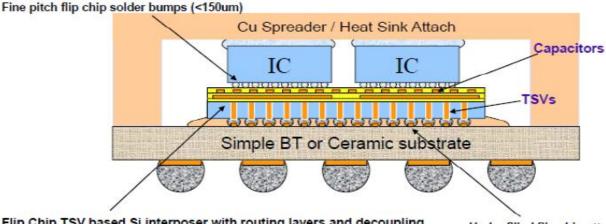

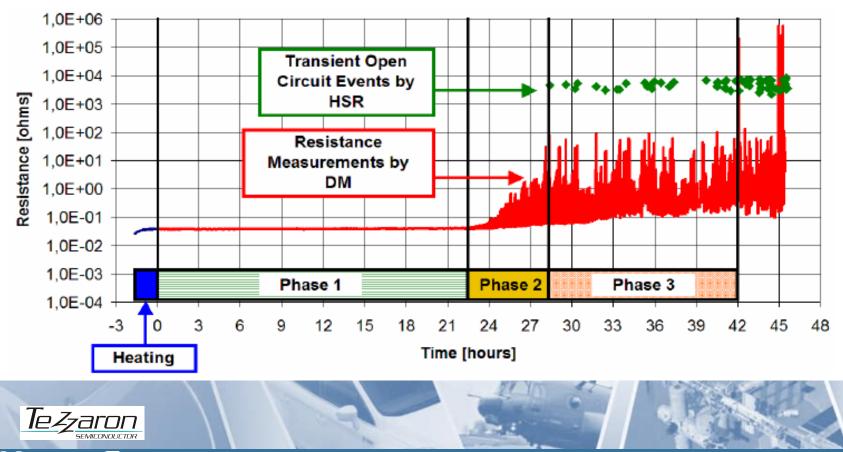

# Mechanisms of Failure

- Fatigue fractures (cracks) are caused by thermo-mechanical stress/strain

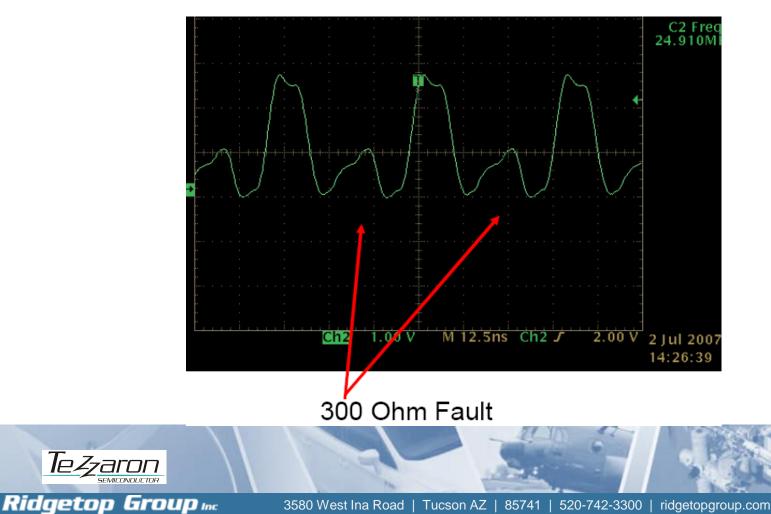

- During periods of high stress, fractured bumps tend to momentarily open and cause intermittent faults of high resistance for periods of ns to µs

- Over time, contamination and oxidation films occur on the fractured faces: the effective contact area becomes smaller and smaller

- Transient opens can be detected by event detectors

**Ridgetop Group**

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

N.

# **Mechanics of Failure**

### HALT results - Pulled FPGA – Damaged Solder Balls

Undamaged

Damaged: Cracked

Cracked, not detectable

Fractured, detectable

**Ridgetop Group** Inc

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

9

₩.

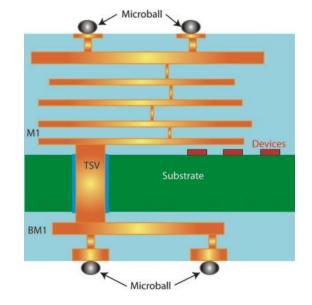

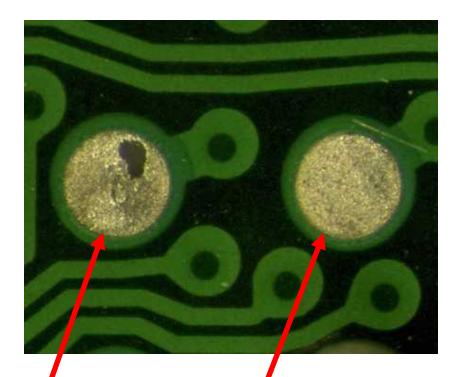

# Increased Complexity : 2.5D IC Interposer

#### Si-BT Flip Chip Interposer

#### Flip Chip TSV Silicon Interposer

- TSV

- Interconnect layers on one side or both sides

- Cu/Pi interconnect layers on one surface (5 um lines/spaces)

- CMOS backend layers (1um lines and spaces) with Backside TSV

- Built in Capacitor (1500 nF/cm2 +)

- Solder Bump or Cu Pillar on the backside

- Smallest (Chip Size) Interposer for Cost and Reliability

Flip Chip TSV based Si interposer with routing layers and decoupling capacitors (1500nf/cm2 +)

Under filled flip chip attach

# 2.5D interconnection challenges

- Undesired side effects of 2.5D ICs

- Increased density → increased heat → degradation and defects

- Qualification/testing is very difficult and expensive

- Confidence in 2.5D IC interconnect reliability must be raised

- Techniques for anticipating failure do not currently exist

- Boundary scan standards for assembly testing are emerging but...

- Boundary scan doesn't address active *in situ* reliability issues

- Net effect on adopting 2.5D IC technology:

- High level of preventive maintenance whenever possible

- Avoidance when such maintenance is not possible, practical, or economical

**Ridgetop Group**

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

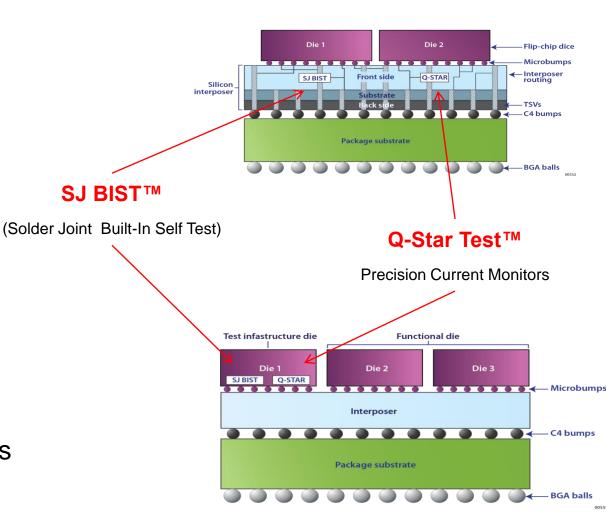

# Ridgetop 2.5D/3D IC Reliability System

- Proven BIST methodologies

- Real-time monitoring of interconnection integrity

- Monitors degradation

- Warns of impending failure (prognostic "canary cell")

- Detects and identifies intermittencies

- Covers both analog and digital signals

- Two alternate approaches (discussed in detail later)

# Through-Silicon Via Built-In Self-Test (TSV BIST) Detection Approaches

SJ BIST Q-Star Test PG-Mon

And, by the way... TSV BIST monitors apply to other stacked die or multi-chip packaging approaches as well

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

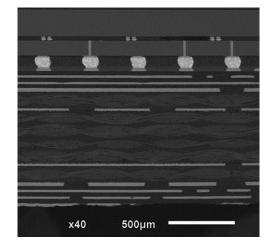

## Intermittent Faults in Components

- Faults are intermittent: confirmed by CAVE, Auburn Univ., German automobile manufacturer

- Occur during periods of increasing strain

- Multiple occurrences per cycle

- Industry standard: 200 ohms +, 200 ns +

**Ridgetop Group**

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

14

₩.

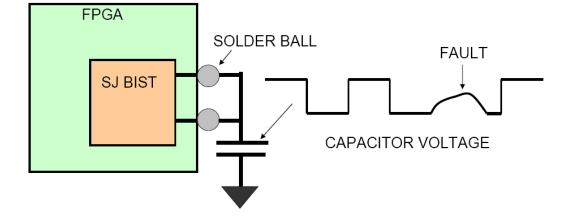

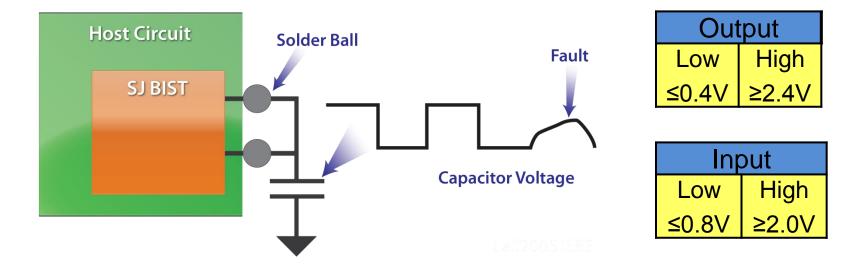

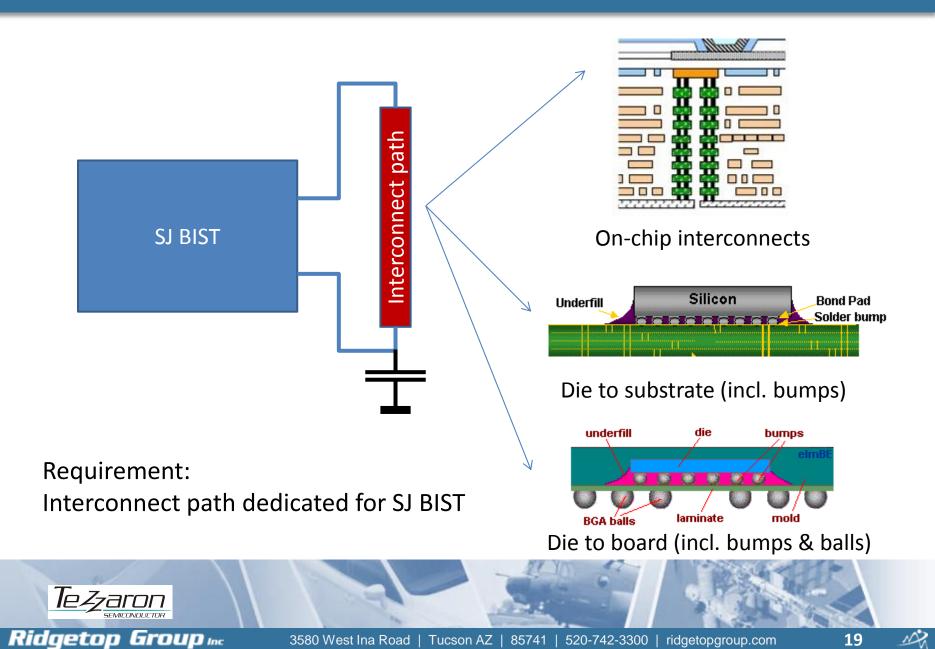

### What is SJ BIST?

- SJ BIST = Solder Joint Built-in Self-Test

- Original solution enabling the verification and validation of solder joint interconnect reliability

- Originally developed for FPGA-BGA applications

- Can be applied to validate the integrity and reliability of any type of interconnection

- Can be instantiated via Verilog or VHDL for FPGAs

- Software Executable version for CPUs

Ridgetop Group Inc

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

N

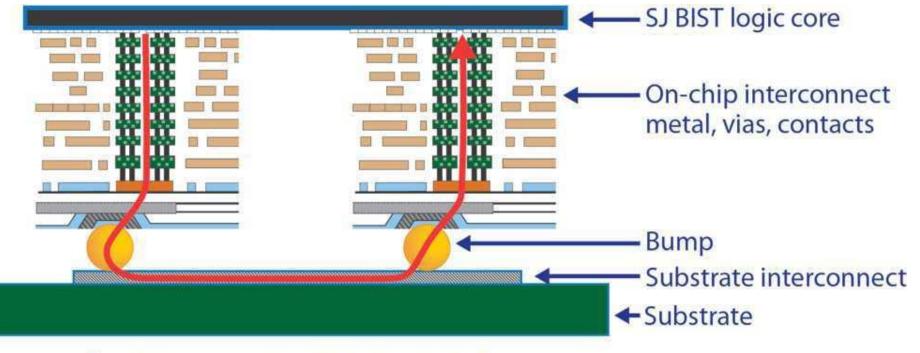

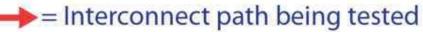

# SJ BIST Implementation – Fault Sensor

- Verilog firmware core

- Each core tests two I/O pins

- Pins are externally wired together

- Small capacitor connected to the two pins

|    | 1 |   | 3 |   | 5        |   | 7 |   | 9 |    | 11 |    | 13       |    | 15 |    | 17 | _  | 19 |    | 21 |    | 23 |    | 25 |    | 27 |    | 29 |          | 31 |    | 33 |     |    | - |

|----|---|---|---|---|----------|---|---|---|---|----|----|----|----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----------|----|----|----|-----|----|---|

|    |   | 2 |   | 4 |          | 6 |   | 8 |   | 10 |    | 12 |          | 14 |    | 16 |    | 18 |    | 20 |    | 22 |    | 24 |    | 26 |    | 28 |    | 30       |    | 32 |    | 34  |    |   |

| _  |   | _ | _ | _ | _        | _ | _ | _ |   | _  | _  | _  | _        | _  | _  | _  |    | _  | -  | _  | _  | _  | _  |    | _  | _  | _  | _  |    | _        | _  | _  | _  | _   | -  | _ |

| A  | 0 | 0 | 0 | 0 | 0        | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0        | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0        | 0  | 0  | 0  | 0   | 1  |   |

| в  | 0 | 0 | 0 | 0 | 0        | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0        | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0        | 0  | 0  | 0  | 0   | 2  |   |

| С  | 0 | 0 | 0 | 0 | 0        | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0        | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0        | 0  | 0  | 0  | 0   | 3  |   |

| D  |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 4  |   |

| Е  |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 5  |   |

| F  |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 6  |   |

| G  | 0 | 0 | 0 | 0 | 0        | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0        | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0        | 0  | 0  | 0  | 0   | 7  |   |

| н  |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 8  |   |

| J  |   | - | - | - | _        | - | - | - | - | -  | -  | _  | -        | -  | -  | -  | -  | _  | 0  | Ξ. | -  | -  | -  | -  | -  | -  | _  | -  | -  | -        | -  | _  | -  |     | 9  |   |

| к  | - | - | - | - | _        | - | - | - | - | -  | -  | _  | -        | -  | -  | -  | -  | -  | 0  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -        | -  | -  | -  | -   | 10 |   |

| L  | - |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 11 |   |

| м  |   |   |   | - |          | _ | - |   |   |    | -  |    | _        |    |    | _  |    | _  | 0  | _  |    |    | _  |    | _  |    | _  | -  |    | -        | -  | _  | -  |     | 12 |   |

| N  |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 13 |   |

| Р  |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 14 |   |

| R  |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 15 |   |

| Т  | _ |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 16 |   |

| U  |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 17 |   |

| V  |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 18 |   |

| W  |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 19 |   |

| Y  |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 20 |   |

| AA |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 2  |   |

| AB |   |   |   |   |          | _ | - |   |   |    |    |    | _        |    |    | _  |    | _  | 0  | _  |    |    | _  |    | -  |    |    | -  |    | -        |    | _  |    |     | 2  |   |

| AC |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 2  |   |

| AD |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 24 |   |

| AE |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     |    |   |

| AF |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 26 |   |

| AG |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 2  |   |

| AH |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 22 |   |

| AJ |   | _ | _ | _ | _        | _ | _ | _ | _ | _  | _  | _  | -        | _  | _  | -  | _  | _  | 0  | _  | _  | _  | _  | _  | _  | _  | _  | _  | -  | -        | _  | _  | -  |     | 30 |   |

| AL |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 31 |   |

| AL |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 3  |   |

| AM |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | 0  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 3  |   |

| AN |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    | ŏ  |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     | 34 |   |

| AP |   | Ľ | 2 | 3 | <u> </u> | 2 | 2 | Ľ | Ľ | Ľ  | Ľ  | 3  | <u> </u> | 3  | 2  | _  | Ľ  | -  | 3  | 9  | 2  | Ľ  | Ľ  | Ľ  | 2  | Ľ  | Ľ  | 2  | 2  | <u> </u> | Ľ  | 2  | 2  | Ľ., | 3  | - |

|    |   |   |   |   |          |   |   |   |   |    |    |    |          |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |          |    |    |    |     |    |   |

TOP VIEW

### SJ BIST Results

# LVTTL – Low Voltage TTL

# SJ BIST Background

- Heritage

- In situ interconnect reliability testing of high pin-count FPGAs in BGA packages

- Originally developed for DoD & NASA space applications

- Proven and reliable

- Easy to deploy

- Highly sensitive to intermittencies and faults

Tunable for different operating frequencies

- No "false positive" flags

- Extended to high density digital interconnection environment, i.e., 2.5D/3D ICs

Ridgetop Group Inc

NZ,

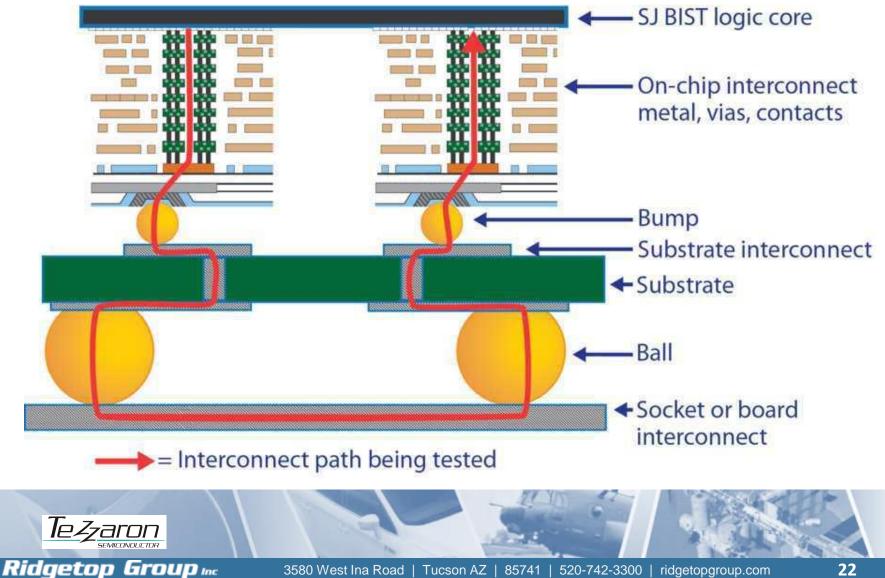

### Testing Die to Substrate

### Testing On-chip Interconnect

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

### Testing Die to Board

22

₩.

# SJ BIST Application Results

- Independent test results by German automotive firm

- Confirmed the same results as obtained by Ridgetop Group

- No false alarms

23

₩.

# Q-Star Test PG-Mon Precision Current Measurement Approach

**Ridgetop Group** Inc.

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

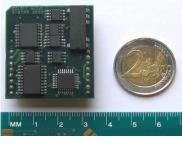

## **Precision Current Measurements**

- Q-Star Test current monitors

- Modules

- →Packaged part testing, lab characterization, failure analysis

Q-Star QD-1011 monitor

- $\rightarrow$ I<sub>DDQ</sub>, I<sub>DDT</sub>, I<sub>SSQ</sub>, power profiling, etc.

- On-chip monitors

- →PG-Mon: validates power, ground, and other connections

- →T-Mon: monitors transient currents

**Q-Star PG-Mon**

Ridgetop Group Inc

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

# Precision Current Measurement : Q-Star Test

- I<sub>DDQ</sub>, I<sub>DDT</sub>, I<sub>SSQ</sub> and other precision picoamp level current measurement instruments for characterization and test

- On-board modules and on-chip sensors

- Test and DFT consulting and training services

- 70 semiconductor companies and 800 instruments installed

- Developed by Ridgetop Europe

**Ridgetop Group** Inc.

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

26

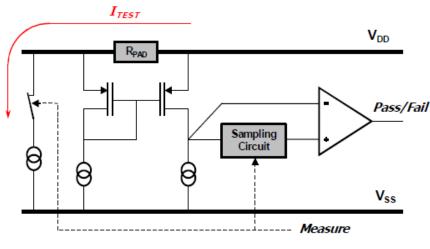

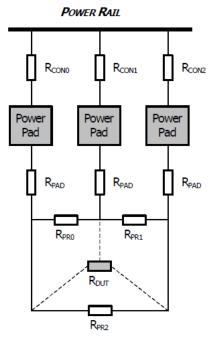

# **PG-Mon Application 1**

- On-chip I/O and power/ground connection verification

- Highly sensitive  $(1.5 4\Omega)$ , non-intrusive observation of signals

**Example:**

### **VDD Monitor Block Schematic**

**Example:**

**IC Power Distribution Network**

**Reliability Monitoring**

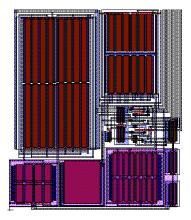

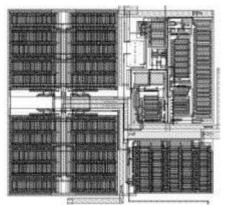

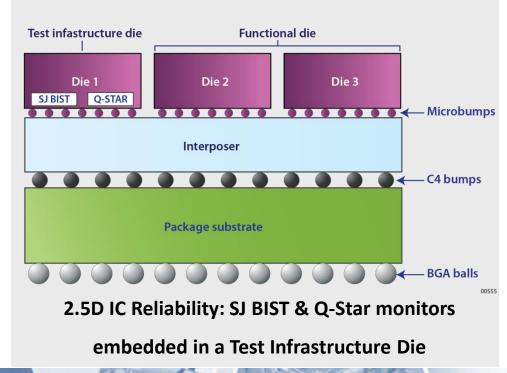

# 2.5D IC Reliability: Test Infrastructure Die

- "Test Infrastructure" die: Connects to strategic traces routed through the interposer

- Most critical functionality

- Most sensitive to degradation (e.g., corners or centers of Die 2 or Die 3)

- Can monitor many signals

- SJ BIST/Q-Star IP embedded in Test Infrastructure die

- Advantages

- Minimizes interposer overhead

- Low cost IC

- Upgrades are simple

- Disadvantages

- Extra interposer real estate

- Distance from some signals

#### **Ridgetop Group**

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

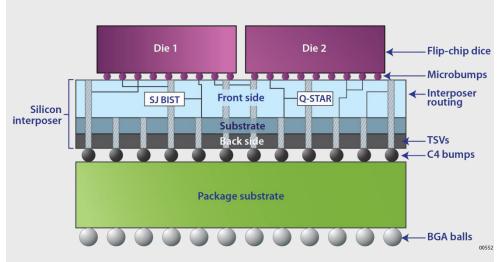

# 2.5D IC Reliability: Interposer-hosted

- Directly hosted on Interposer: Connects to strategic traces routed through the interposer

- Most critical functionality

- Most sensitive to degradation (e.g., corners or centers of Die 2 or Die 3)

- Can monitor many signals

- SJ BIST/Q-Star IP embedded in Silicon Interposer

- Advantages

- Minimizes interposer overhead

- Monitors near key signals

- Disadvantages

- Interposer cost is higher

- Signal routing may be trickier

### 2.5D IC Reliability: SJ BIST & Q-Star monitors embedded in Silicon Interposer

#### **Ridgetop Group**

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

$\sim$

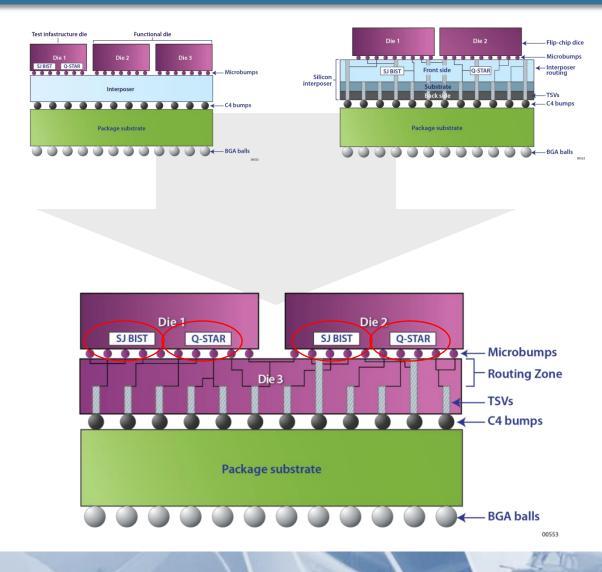

# From 2.5D IC to 3D IC Reliability Monitoring

- 3D IC migration: Embed SJ BIST / PG-Mon IP in TSVenabled ICs

- Required when no interposer present Highest quality monitoring

- Reduces cost and overhead

- Standardized approach for broadest applicability

30

N.

### Summary

- 2.5D / 3D IC technologies pose new challenges

- Reliability assurance requires more than traditional test

- Real-time TSV BIST monitors...

- Detect intermittencies

- Identify degradation before failure

- Are non-intrusive

Ridgetop Group Inc.

N

# About Ridgetop Group, Inc.

- Incorporated in 2000, and headquartered in Tucson, AZ. Ridgetop Europe established in 2010 in Belgium.

- Microelectronic Design and Test Solutions:

- SJ BIST<sup>™</sup> Based Test Solutions

- ProChek<sup>™</sup> Semiconductor Characterization System

- Q-Star Test<sup>™</sup> Precision Current Measurement Instruments

- PDKChek<sup>™</sup> In-Situ Test Structures

- ISO:9001/AS9100C-compliant Design and Integration Services

- Strong market position with commercial and government customers in USA, Canada, Europe, and Asia

Ridgetop Group Facilities in Tucson, AZ

Ridgetop Europe Facilities in Brugge, Belgium

#### **Ridgetop Group**

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

32

NZ,

# **Contact Information**

## Ridgetop Group Inc.

Andrew Levy VP Business Development

<u>alevy@RidgetopGroup.com</u> (office) +1 520-742-3300 x115 (mobile) +1 503-320-5466

3580 West Ina Road Tucson, AZ 85741

**Ridgetop Group**

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

33

*M*≩

# Upcoming Webinars

| Торіс                                                                           | Date              | Time               |  |  |  |

|---------------------------------------------------------------------------------|-------------------|--------------------|--|--|--|

| Reliable Electronics? Precise Current<br>Measurements May Tell You<br>Otherwise | September 9, 2014 | 8:00 – 9:00 AM PDT |  |  |  |

| Intermittent Fault Detection in Circuit<br>Boards and Connectors                | October 8, 2014   | 8:00 – 9:00 AM PDT |  |  |  |

For more information about Ridgetop Group webinars, email us at information@ridgetopgroup.com

**Ridgetop Group** Inc

3580 West Ina Road | Tucson AZ | 85741 | 520-742-3300 | ridgetopgroup.com

11 k

# **Questions?**

- Slides and recording of the webinar will be available shortly via an e-mail from Ridgetop

- E-mail follow-up questions & comments to

- Tezzaron: David Chapman, <u>dchapman@tezzaron.com</u>

- Ridgetop: Andrew Levy, <u>alevy@ridgetopgroup.com</u>

- Please fill out our brief feedback survey at: <u>https://www.surveymonkey.com/s/FDJ9MQH</u>

# Thanks for your time and interest!

**Ridgetop Group**

N